Low-Level Projects

Personal

PCB Power Converter (GitHub)

- 5V to 3.3V low dropout regulator created in Altium.

- Utilized 2 GST-GH connectors to create an external-to-external voltage converter.

Result: Increased schematic capture, PCB routing, and Git proficiency.

Academic

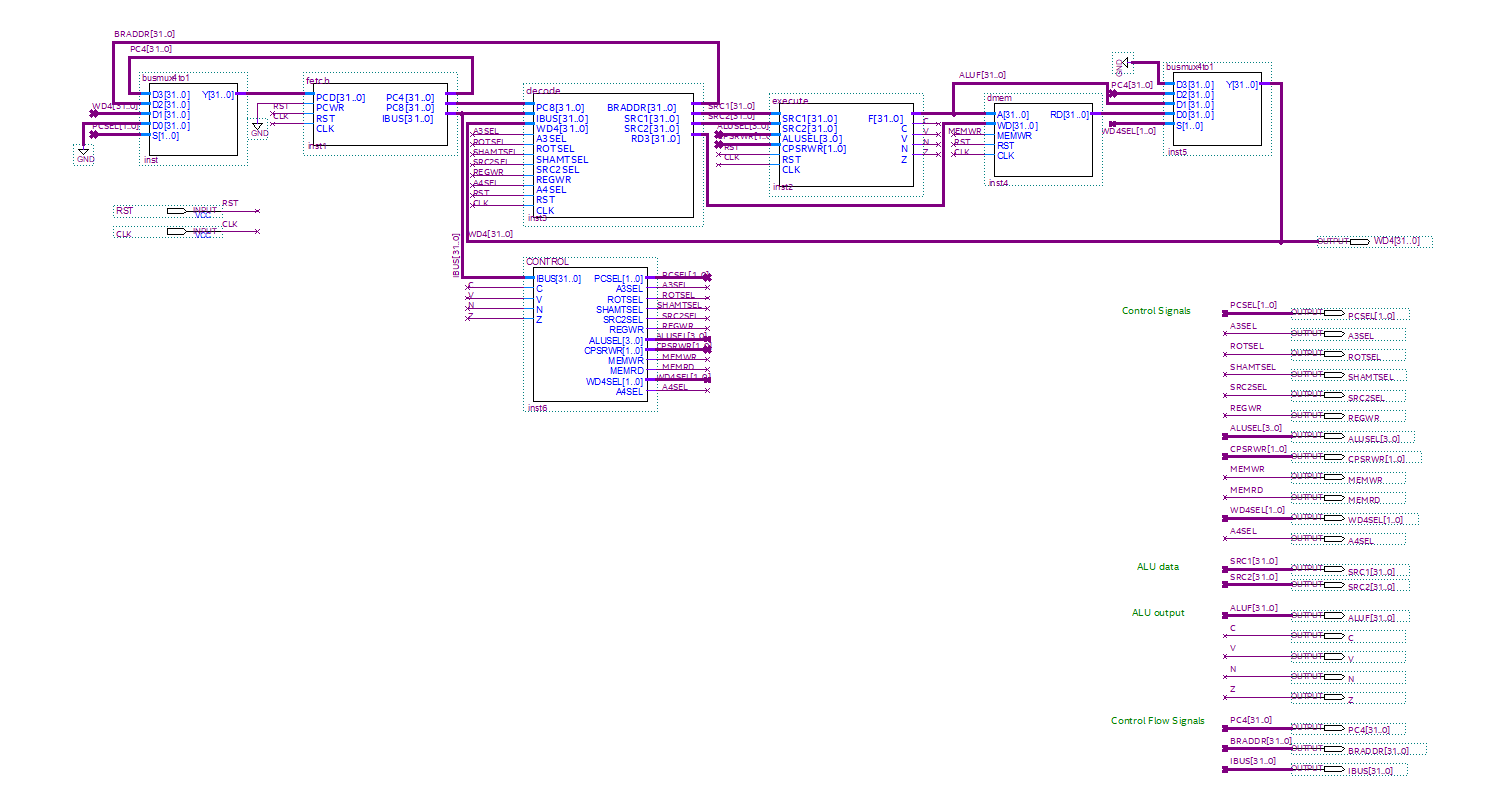

Single Cycle Processor (GitHub)

- ARMv4 32-bit michroarchitecture implemented in VHDL.

- Program processes an ARMv4 assembly instruction set 1 instruction at a time (single cycle).

- Architecture enables data processing, loading/storing, and branching.

- Each instruction goes through the instruction cycle (fetch, decode, execute, memory, writeback)

- Loops, arithmetic, and functions can be implemented in the instruction set.

Result: Created a simple computer. Broadened VHDL and Git proficiency as well as understanding of computer microarchitecture

Usage: User can create assembly instruction sets for programming hardware.

Instruction Processor (GitHub)

- 8-bit saturating up binary counter with an editable instruction ROM. (VHDL)

- Programmed onto a Digi-Bot, an Intel MAX10 DE-10 Lite-based robot car with two motor-backed wheels and an infrared line sensor.

- Uses a Mealy machine to iterate through a counter and, in parallel, an instruction set created by the programmer. Instructions decoded via decoder.

- Utilized sequential logic instead of combinational logic, the former having memory-based logic instead of reactive.

- Digi-Bot reads the instruction ROM and displays the corresponding instruction on a maximum of 6 7 segment LEDs

Result: Mimicked the essence of the function of a Microcontroller (sequential logic) using the Mealy machine. Broadened VHDL, FPGA, and Git proficiency.

Usage: User can manually alter the instruction ROM so that the Digi-Bot can serially perform movements and sounds as desired.

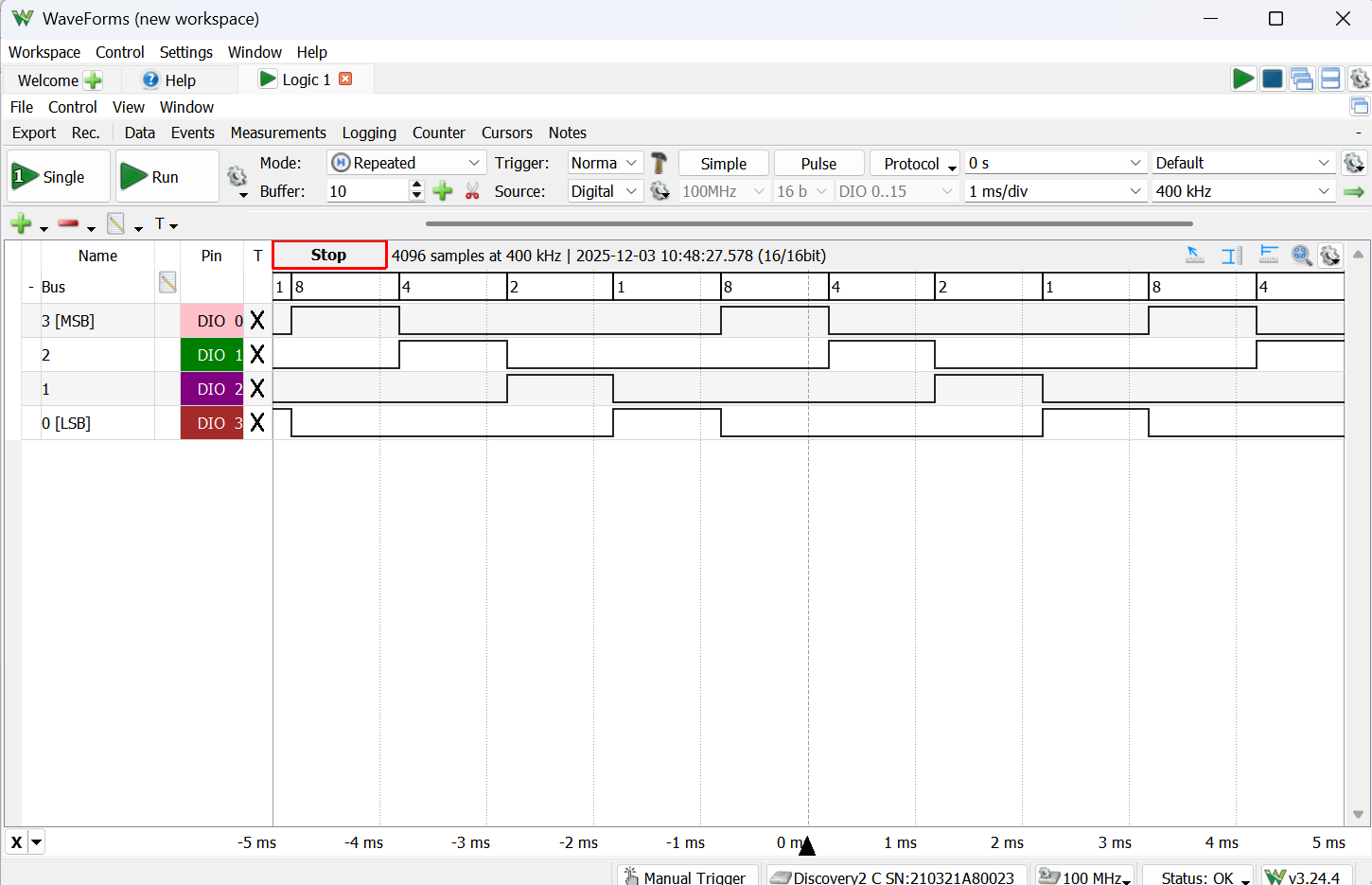

4-Cylinder Engine Controller (GitHub)

- Modulo-4 nonsaturating down binary counter. (VHDL)

- Programmed onto an Intel MAX10 DE-10 Lite FPGA with sequential logic.

- Project is a Moore machine using edge-triggered logic. Simulated in WaveForms.

- Utilizes sequential logic instead of combinational logic, the former having memory-based logic instead of reactive.

Result: Demonstrated the benefit of sequential logic which enables state retention and memory-dependent system behavior. Reinforced VHDL, FPGA, and Git skills.

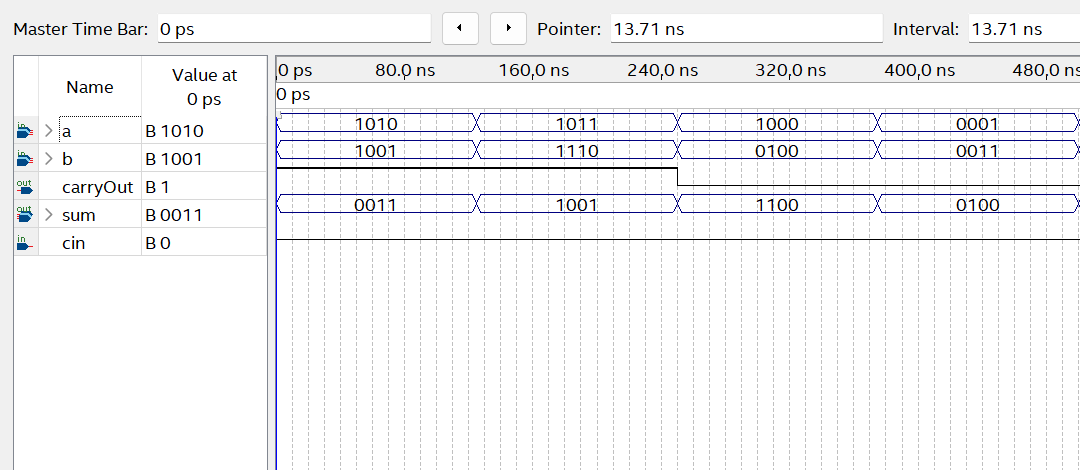

Carry Look-Ahead Adder (GitHub)

- Program which adds 2 4-bit numbers together with O(1) time complexity on an FPGA. (VHDL)

- Programmed onto an Intel MAX10 DE-10 Lite FPGA with combinational logic.

- Carry calculator used in substitution of the ripple carry style as the latter possesses O(n) time complexity.

- The DE-10 Lite was programmed to take 9 switch inputs (a, b, cin) and produce 4 LED outputs.

Result: Amplified VHDL, FPGA, and Git fundamentals.

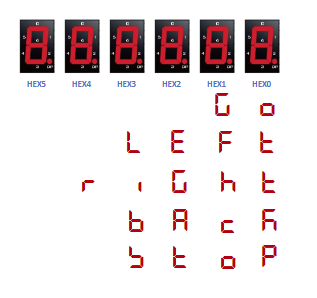

7-Segment Decoder (GitHub)

- Program which displays the current instruction of the Digi-Bot. Implemented on an FPGA. (VHDL)

- Programmed onto a Digi-Bot, an Intel MAX10 DE-10 Lite-based robot car with two motor-backed wheels and an infrared line sensor.

- The Digi-Bot was programmed with combinational logic to follow a black line and stop at a collision.

- A maximum of 6 7-segment (8 bit) LEDs used for the display and a 3-bit logic vector for the motors and collsion sensor.

Result: Increased VHDL, block diagram routing, and Git proficiency.